#### **IWES 2017**

#### 2nd Italian Workshop on Embedded Systems

Rome – 7-8 September 2017

#### **UNISI Research Group Overview**

**Roberto Giorgi University of Siena, Italy**

http://www.dii.unisi.it/~giorgi

#### **Engineering Faculty in Siena**

#### **Computer Architecture Lab**

#### **Research Group** @ UNISI

- 1 Associate prof.: Roberto Giorgi + 1 Aggregate prof.: Sandro Bartolini

- Cooperation with prof. Antonio Rizzo

- 1 PhD Student, 1 Kernel Hacker, 1 Grant research student

- HR Throughput: 2 Full-Prof., 2 Researchers, 9 Postdocs, 7 PhD students ---- during the last 7 years

- Courses by me:

- Bachelor (L1): **Computer Architecture** (6 credits) -3<sup>rd</sup> year (Italian)

- Master (L2): High Performance Computer Architecture (9 credits) 1<sup>st</sup> and 2<sup>nd</sup> year(English)

#### Lab Resources

- 64-core (x86) CC-NUMA w/1024GiB RAM

- 48-core+256GiB, about 15 simulation servers (8-core+32GiB)

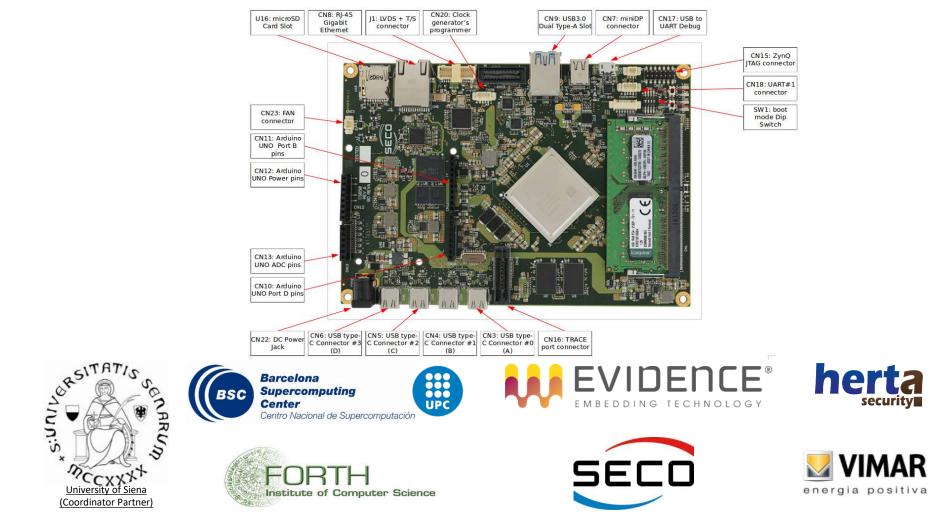

- 12 different FPGA boards ranging from Virtex-6 to Zynq Ultrascale+ (6-core 64 bits)

- Xeon Phi, Maxeler Dataflow computer, GPUs, 50+ embedded boards, (20+ workstations)

#### Cooperation with Laboratorio Nazionale Embedded Systems and Smart Manufacturing (LN-ESSM) CINI

- CINI lab LN-ESSM (in progress) director prof. Antonino Mazzeo

- UNISI competences

- (Giorgi, Bartolini) Programmable Hardware, Processors, Co-processors and Microcontrollers

- Giorgi) Hardware/software projects ecosystems

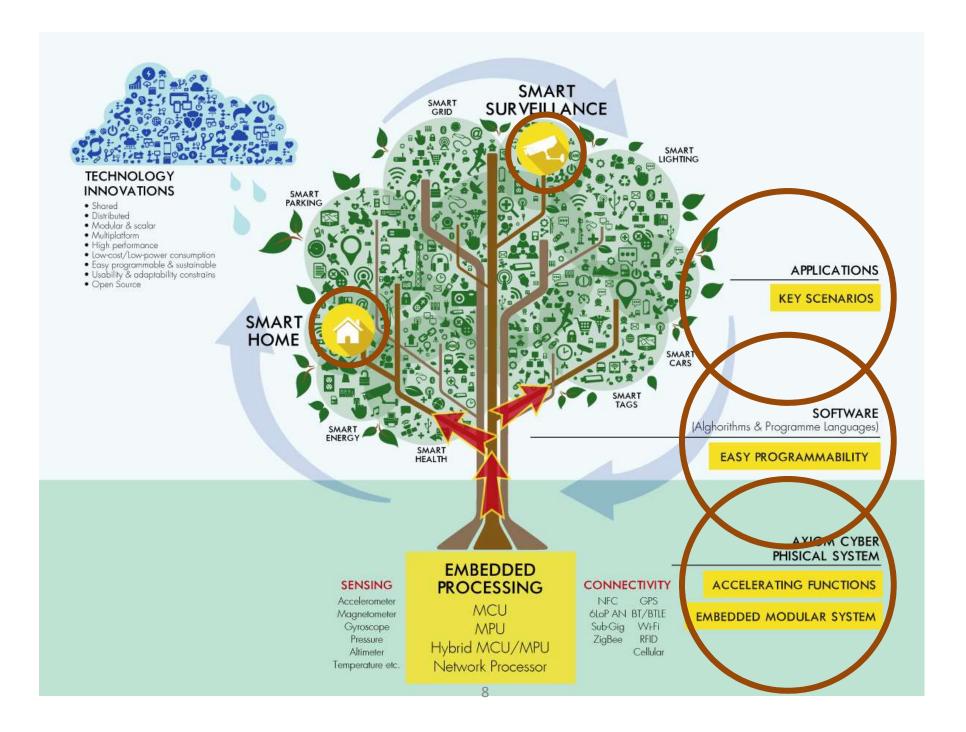

- (Giorgi) Smart Cyber-Physical Systems architectures

- Giorgi, Rizzo) Smart Systems Integration and Internet of Things Applications

- (Rizzo) Human Machine Interface

- (Bartolini) Efficient programmability of heterogeneous multi-/many-core systems with single source code

- (Bartolini) Hardware and software for security and trust

- (Bartolini) Energy Management, power efficiency and approximate computing in embedded nodes

#

#### Agile, eXtensible, fast I/O Module for the cyber-physical era

×

2015-2017 -- 4Meuro funding Coordinator: Roberto Giorgi

#### FUTURE AND EMERGING TECHNOLOGIES 6.13 Meuro funding 2010-13

Università di Siena (Coordinator)

Barcelona Supercomputing Center

INRIA

#### **Exploiting Dataflow Parallelism in Teradevice Computing**

http://teraflux.eu

Contact: Prof. Roberto Giorgi (project coordinator): http://www.dii.unisi.it/~giorgi

University of Augsburg

University of Manchester

University of Delaware (USA)

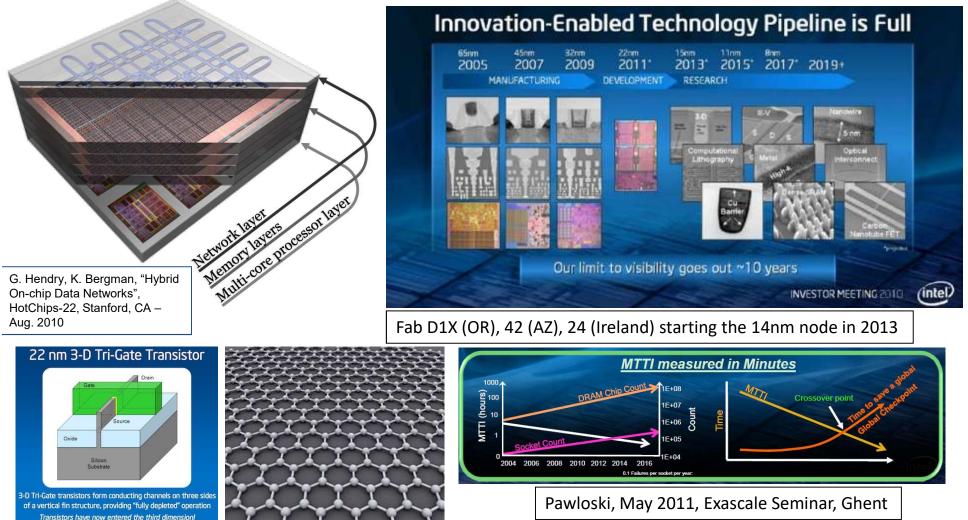

## (Nearer) Future Scenarios == 3D stacking, 8nm, 3D transistors, Graphene

ERA Embedded Reconfigurable Architectures

Project number: 249059

FP7 – 2010-2013 -- ~ 3 Meuro funding

#### ERA TARGET SYSTEM

- Smartphone with FPGA-based SoCs (e.g Zynq)

- Exploring the energy efficiency of reconfigurable hardware

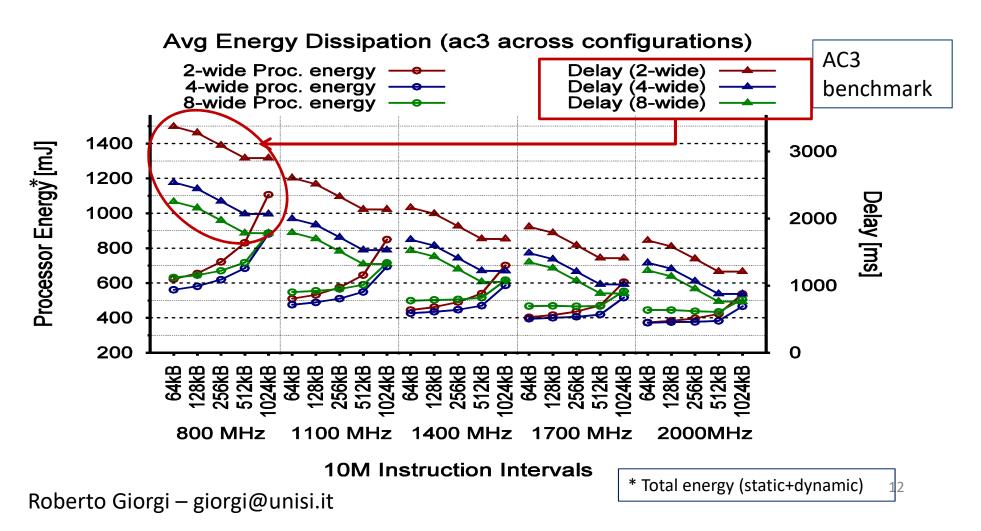

#### Benchmarks analysis from energy+delay viewpoint

- DYNAMYC ENERGY consumption and DELAY while varying L2 cache-size, issue-width, frequency

- Delay significantly decreases with L2 cache size, frequency, issue-width (total energy as in previous slide)

- These behaviors have been confirmed across all the EBS applications

### Cooperation with SantaChiaraLab (100m from us), Dept. Cognitive Science (in-building) & SECO (Arezzo)

SECO/UNISI achievements:

− 2014: UDOO-ARM (99 \$ PC+Arduino)  $\rightarrow$  600k\$ on Kickstarter

- 2016: UDOO-x86 (PC+Arduino, 10x faster than Raspberry-3) → 800k\$ on Kickstarter

- Selected among the finalists of the EU "Innovation Radar Prize" (Sep. 2016)

#### **UNIVERSITY OF SIENA – ROBERTO GIORGI**

## Thanks for your attention!