Design of Energy/Quality Scalable Hardware By Runtime Voltage Scaling and Back Biasing

#### **Daniele Jahier Pagliari**

EDA Group Politecnico di Torino Torino, Italy

TECHNOLOGY RESEARCH INSTITUTE

2nd IWES September 8th , 2017, Rome, Italy

# **The EDA Group**

#### <u>Electronic Design Automation</u>

- 7 Faculty members

- Enrico Macii, Massimo Poncino, Alberto Macii, Andrea Acquaviva

- Elisa Ficarra, Andrea Calimera, Santa Di Cataldo, Sara Vinco

- 4 post-doc researchers

- ~10+ Ph.D. students & Research Assistants

- Three main areas of research:

- EDA (energy efficiency, EES, etc.)

- Technologies for Smart Cities (Buildings, Districts, etc.)

- Bioinformatics

#### Strong record of EU funded projects

30+ in the last 10 years.

#### Background and Motivation

- Dynamic V<sub>DD</sub>/V<sub>BB</sub>/Accuracy Tuning

- Experimental Results

- Conclusions and Future Work

IoT devices trends:

IoT devices trends:

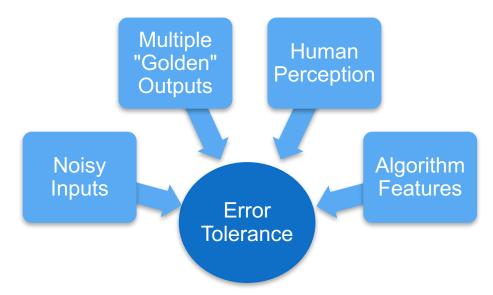

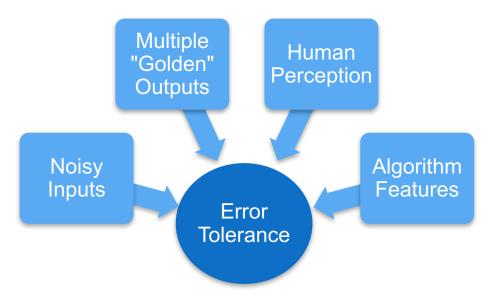

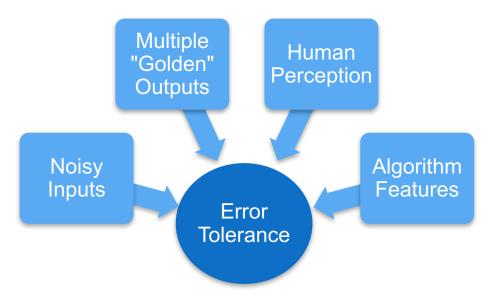

- Many emerging applications are error tolerant ( or error resilient):

- Recognition, Mining and Synthesis (RMS) domains

IoT devices trends:

- Many emerging applications are error tolerant ( or error resilient):

- Recognition, Mining and Synthesis (RMS) domains

IoT devices trends:

- Many emerging applications are error tolerant ( or error resilient):

- Recognition, Mining and Synthesis (RMS) domains

<u>Approximate Paradigm:</u> Tradeoff energy consumption and output quality leveraging applications error tolerance.

IoT devices trends:

- Many emerging applications are error tolerant ( or error resilient):

- Recognition, Mining and Synthesis (RMS) domains

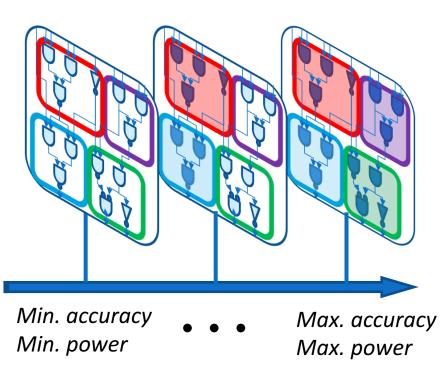

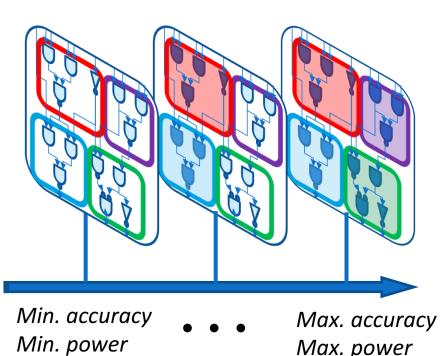

Approximate Paradigm: Tradeoff energy consumption and output quality leveraging applications error tolerance.

- Two main approaches:

- Design-time Approximations

- Quality-Configurable Systems (QCS)

# **Background - Functional Units**

#### **1.** Approximate circuits:

#### Mostly adders and multipliers

Kyaw, Goh and Yeo, EDSSC'10, Huang, Lach and Robins, DAC'12, Farshchi, Saeed and Fakhraie, CADS'13, Jiang, Han and Lombardi, GLSVLSI'15, Bhardwaj, Mane and Henkel, ISQED'15, etc.

#### 2. Approximate synthesis:

#### Generalization of the previous techniques to any netlist

Shin and Gupta, ATS'08, Venkataramani et al, DAC'12, Miao, Gerstlauer and Orshansky, ICCAD'13, Jahier Pagliari et al, ICCD'15,etc. 3. Quality-configurable circuit architectures:

#### Arithmetic units

De la Guya Solaz, Han, Conway, IEEE TCAS'11, Kahng and Kang, DAC'12, Ye et al, ICCAD'13, Liu, Han and Lombardi, DATE'14, etc.

• Voltage scalable meta-functions Mohapatra, Chippa, Raghunathan and Roy, DATE'11

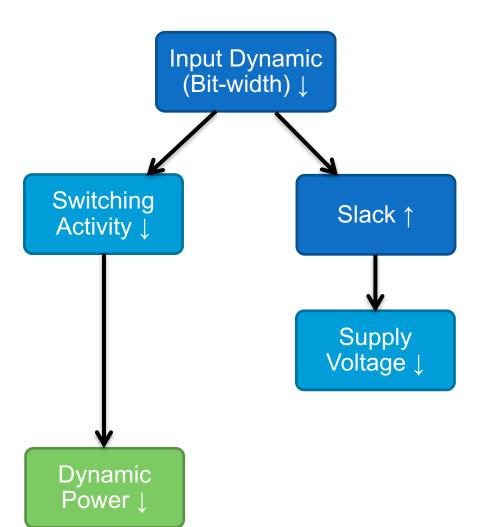

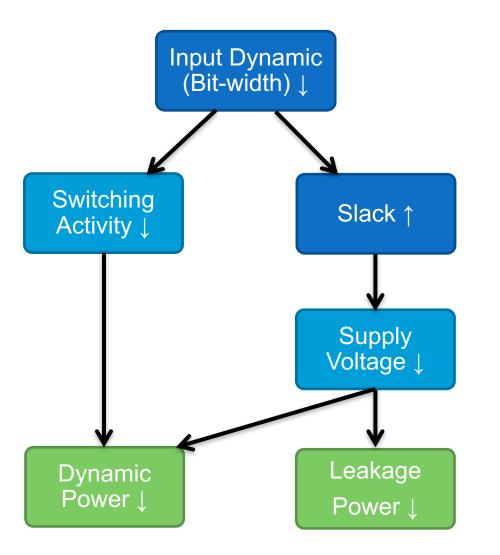

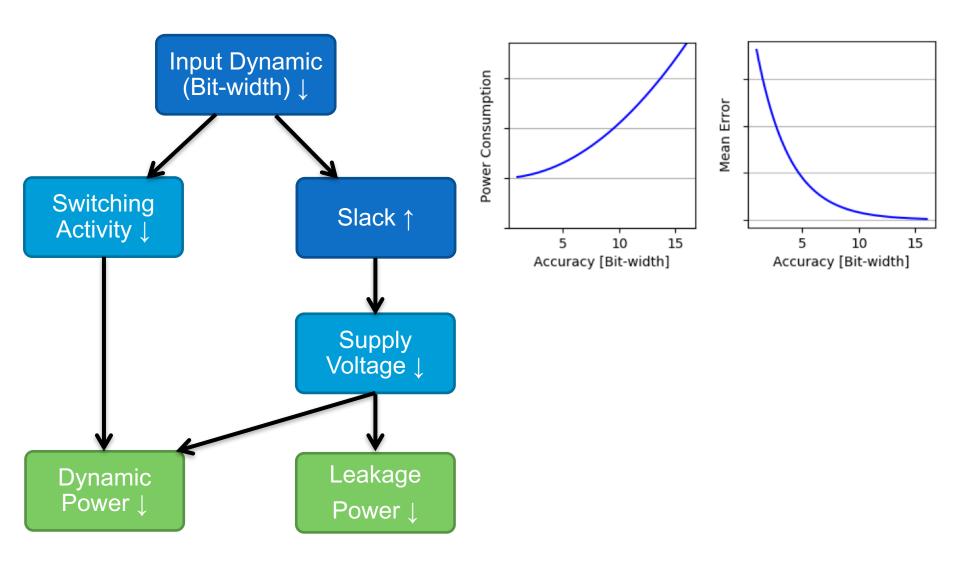

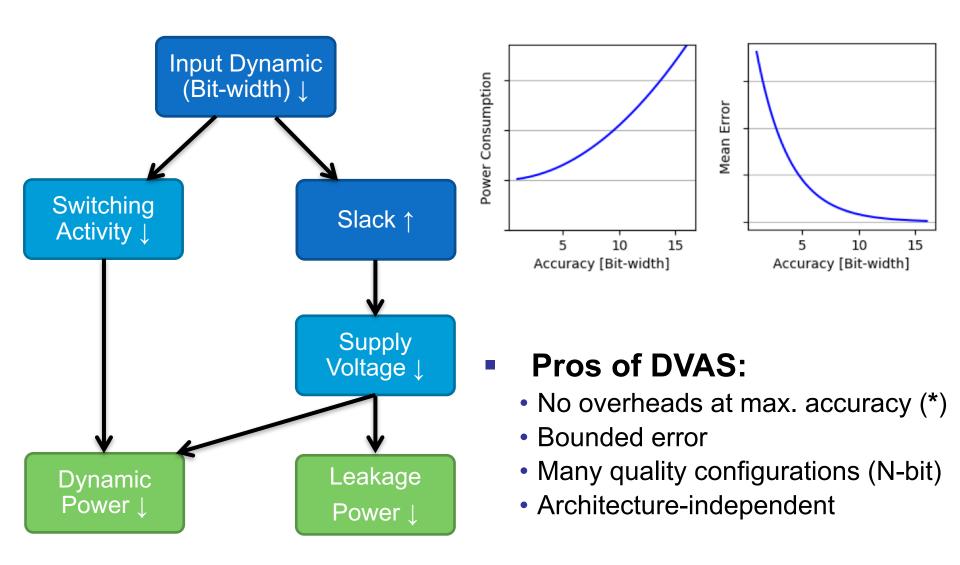

#### 4. Dynamic Voltage and Accuracy Scaling (DVAS):

Use technological knobs only (no design modifications)

Moons and Verhelst, ISLPED'15, Moons et al, ISSCC'17, etc.

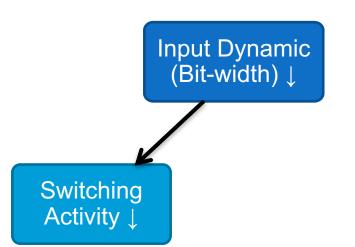

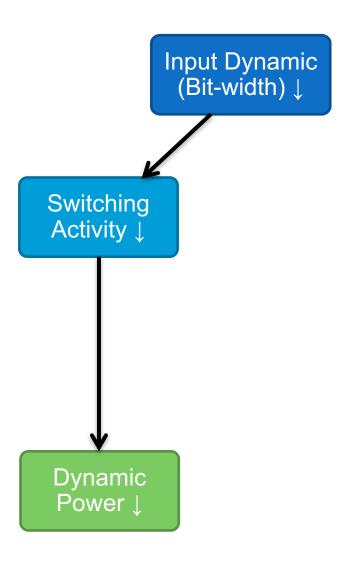

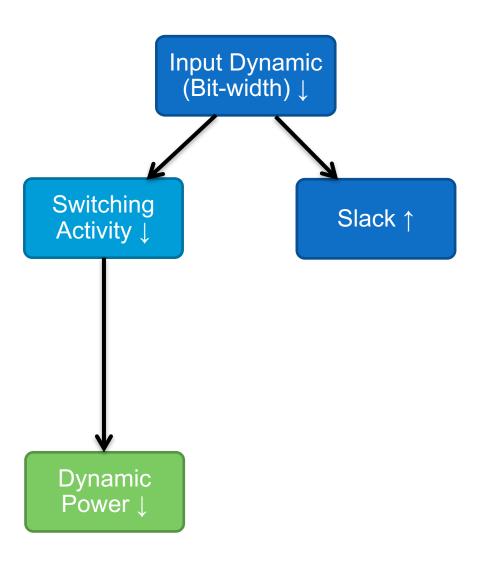

Input Dynamic (Bit-width) ↓

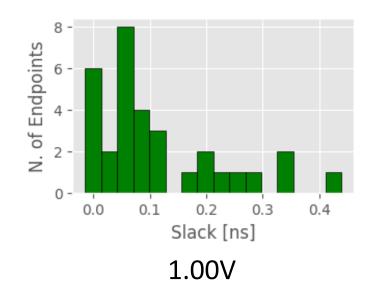

#### Main Limitation of DVAS: "Wall-of-Slack" phenomenon:

- Synthesis optimizes long paths for timing, short ones for area and power

- Most paths become "almostcritical"

# Main Limitation of DVAS: "Wall-of-Slack" phenomenon:

- Synthesis optimizes long paths for timing, short ones for area and power

- Most paths become "almostcritical"

#### • Example:

• Booth multiplier endpoint histogram.

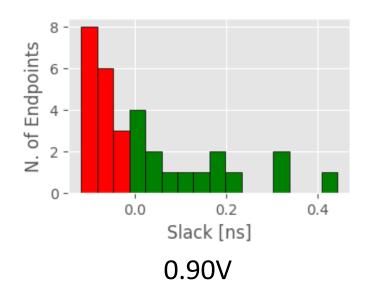

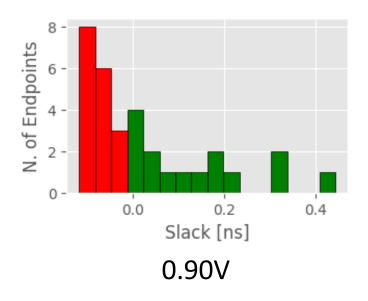

# Main Limitation of DVAS: "Wall-of-Slack" phenomenon:

- Synthesis optimizes long paths for timing, short ones for area and power

- Most paths become "almostcritical"

- When V<sub>DD</sub> is scaled the number of usable bits decreases rapidly

#### • Example:

• Booth multiplier endpoint histogram.

# Main Limitation of DVAS: "Wall-of-Slack" phenomenon:

- Synthesis optimizes long paths for timing, short ones for area and power

- Most paths become "almostcritical"

- When V<sub>DD</sub> is scaled the number of usable bits decreases rapidly

#### • Example:

Booth multiplier endpoint histogram.

Useful bit-width configurations require  $V_{DD} \cong V_{DD,NOM}$

# Motivation (cont'd)

#### **Contrasting the "Wall of Slack":**

#### • **Solution 1:** modify synthesis constraints.

Overhead in area and power at maximum accuracy.

# Motivation (cont'd)

#### Contrasting the "Wall of Slack":

#### Solution 1: modify synthesis constraints.

- Overhead in area and power at maximum accuracy.

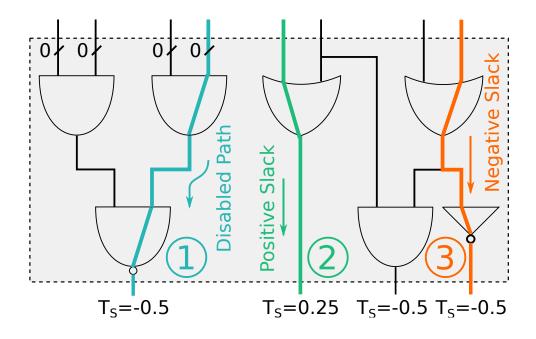

- Solution 2: finer-grain power/delay tuning

- Key: in reduced accuracy "modes", not all paths of the circuit require the same "speed"

- Possible solution: multiple VDD

- Requires level shifters

- Excessive power overheads for a single FU

- Possible solution: multiple VDD

- Requires level shifters

- Excessive power overheads for a single FU

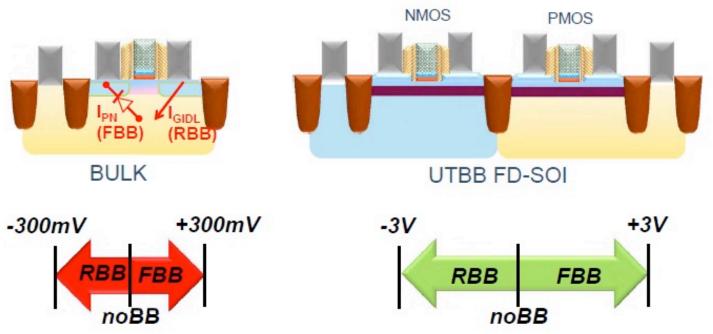

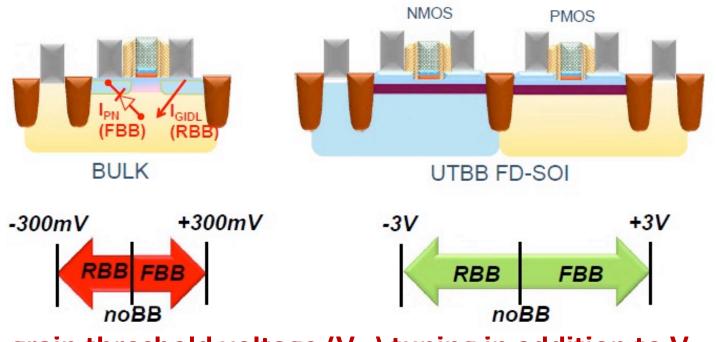

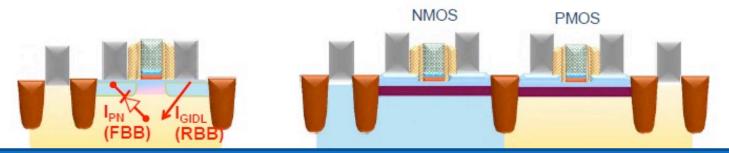

- Our solution: combine DVAS with FDSOI's Back Bias

#### Possible solution: multiple VDD

- Requires level shifters

- Excessive power overheads for a single FU

- Our solution: combine DVAS with FDSOI's Back Bias

#### Possible solution: multiple VDD

- Requires level shifters

- Excessive power overheads for a single FU

- Our solution: combine DVAS with FDSOI's Back Bias

Fine-grain threshold voltage (V<sub>th</sub>) tuning in addition to V<sub>DD</sub> assignment

#### Possible solution: multiple VDD

- Requires level shifters

- Excessive power overheads for a single FU

- Our solution: combine DVAS with FDSOI's Back Bias

#### Advantages:

- Fine-grain speed/power control

- V<sub>DD</sub> possibly shared with other FUs

- No level shifters; Well insulation trenches (area overhead only)

#### assignment

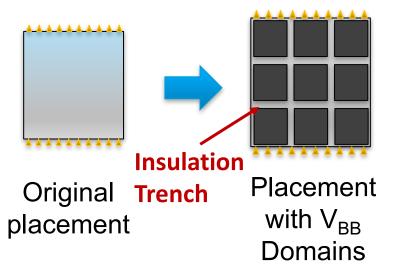

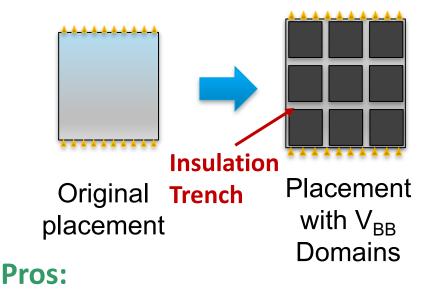

#### **Issue with V<sub>BB</sub> assignment:**

- Cannot apply independent V<sub>BB</sub> to each cell

- Partition in V<sub>BB</sub> domains is required

#### **Issue with V<sub>BB</sub> assignment:**

- Cannot apply independent V<sub>BB</sub> to each cell

- Partition in V<sub>BB</sub> domains is required

#### **Issue with V<sub>BB</sub> assignment:**

- Cannot apply independent V<sub>BB</sub> to each cell

- Partition in V<sub>BB</sub> domains is required

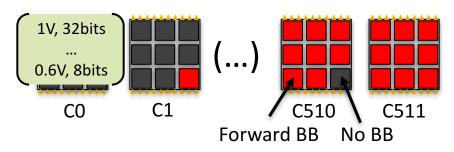

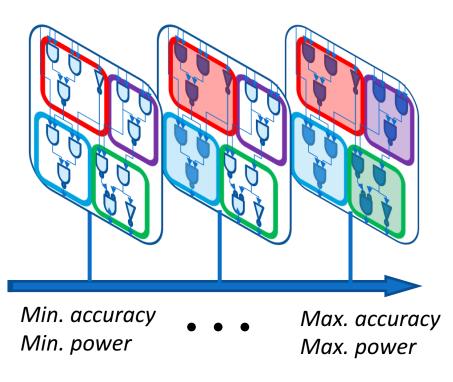

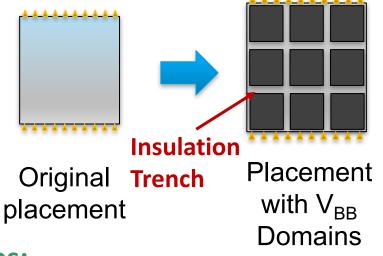

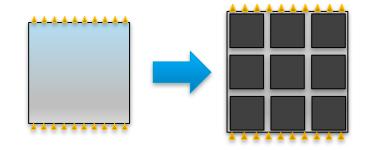

#### Proposed partitioning: Regular Tiling

#### Issue with V<sub>BB</sub> assignment:

- Cannot apply independent V<sub>BB</sub> to each cell

- Partition in V<sub>BB</sub> domains is required

#### Proposed partitioning: Regular Tiling

- Regularity of design

- Easy to incorporate in EDA flow

- Minimal displacement of cells

#### Issue with V<sub>BB</sub> assignment:

- Cannot apply independent V<sub>BB</sub> to each cell

- Partition in V<sub>BB</sub> domains is required

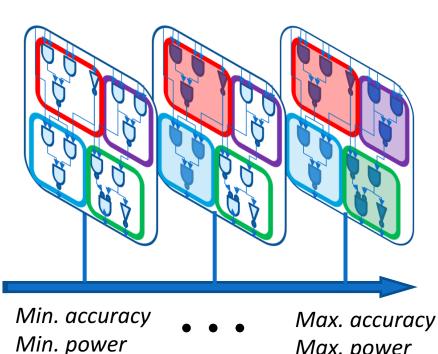

Max. power

#### **Proposed partitioning: Regular Tiling**

#### **Pros:**

- **Regularity of design**

- Easy to incorporate in EDA flow

- Minimal displacement of cells

Minimal timing, area and power overheads at maximum accuracy.

### **Experimental Results**

#### **Designs:**

- Booth multiplier

- FFT Butterfly unit

- 30-tap FIR filter

- 16-bit fixed-point implementations

### **Experimental Results**

#### **Designs:**

- Booth multiplier

- FFT Butterfly unit

- 30-tap FIR filter

- 16-bit fixed-point implementations

#### **Operating Conditions:**

- V<sub>DD</sub> = [0.6V, 0.7V,...1.0V]

- Forward BB: V<sub>BB</sub> = ±1.1V (N-Well/P-Well)

# **Experimental Results**

#### **Designs:**

- Booth multiplier

- FFT Butterfly unit

- 30-tap FIR filter

- 16-bit fixed-point implementations

#### **Operating Conditions:**

- V<sub>DD</sub> = [0.6V, 0.7V,...1.0V]

- Forward BB: V<sub>BB</sub> = ±1.1V (N-Well/P-Well)

| Design    | Area<br>[mm²] | Clock<br>Freq.<br>[GHz] | # of V <sub>BB</sub><br>Domains |

|-----------|---------------|-------------------------|---------------------------------|

| Booth     | 2.59e-03      | 1.25                    | 2 x 2                           |

| Butterfly | 7.71e-03      | 1.00                    | 3 x 3                           |

| FIR       | 9.10e-03      | 0.75                    | 3 x 3                           |

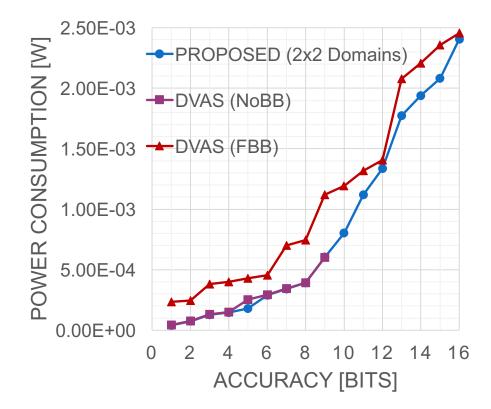

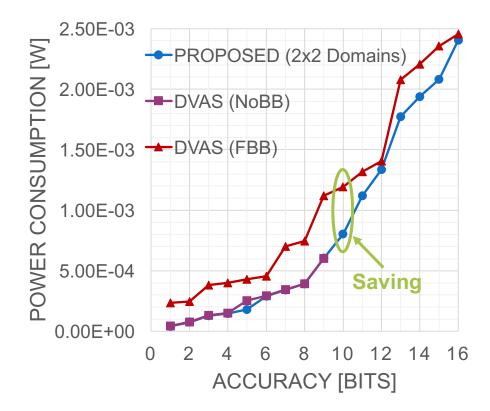

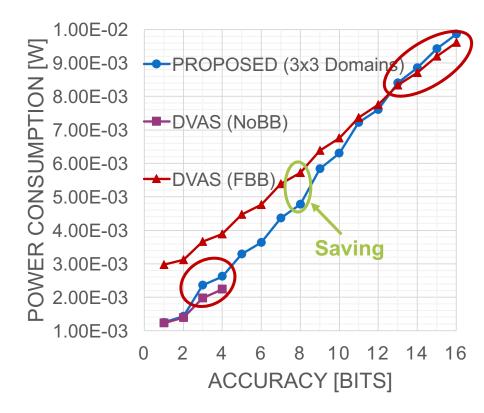

### **Booth Multiplier**

- Plots: Minimum power configuration for each accuracy

- Combining (global) V<sub>DD</sub> scaling and fine-grain back-biasing

### **Booth Multiplier**

- Plots: Minimum power configuration for each accuracy

- Combining (global) V<sub>DD</sub> scaling and fine-grain back-biasing

- Comparison:

- DVAS with No Back Biasing (NoBB)

- DVAS with FBB in the entire circuit

### **Booth Multiplier**

- Plots: Minimum power configuration for each accuracy

- Combining (global) V<sub>DD</sub> scaling and fine-grain back-biasing

- Comparison:

- DVAS with No Back Biasing (NoBB)

- DVAS with FBB in the entire circuit

- 32.7% Saving w.r.t. DVAS @ 10-bit accuracy!

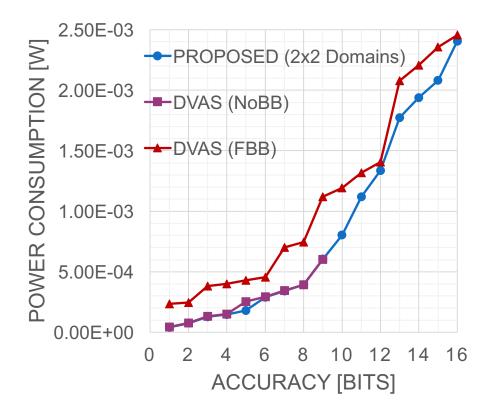

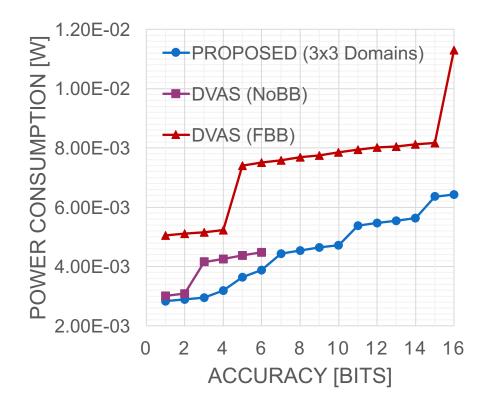

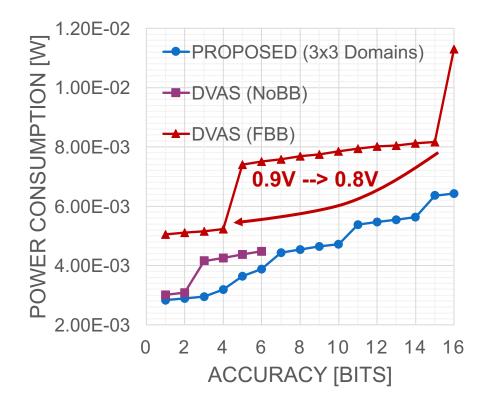

### **FIR Filter**

- "Wall-of-Slack" clearly visible

- Maximum DVAS + FBB accuracy (without violations):

- 15-bit @ 0.9V

- Only 4-bit @ 0.8V!

### **FIR Filter**

- "Wall-of-Slack" clearly visible

- Maximum DVAS + FBB accuracy (without violations):

- 15-bit @ 0.9V

- Only 4-bit @ 0.8V!

### **FIR Filter**

- "Wall-of-Slack" clearly visible

- Maximum DVAS + FBB accuracy (without violations):

- 15-bit @ 0.9V

- Only 4-bit @ 0.8V!

- 39.9% Saving w.r.t. DVAS @ 10-bit accuracy!

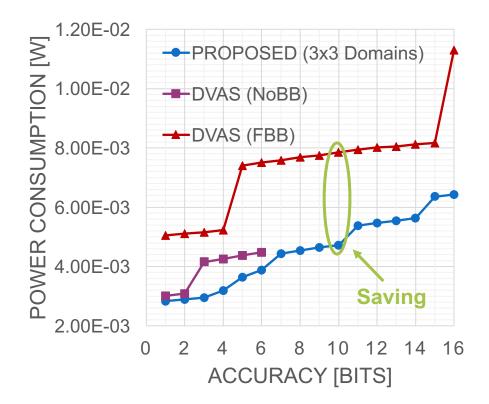

### **FFT Butterfly**

- Large number of V<sub>BB</sub> domains (3 x 3) compared to relatively small circuit area

- Power overheads more significant

- Also, "Wall-of-Slack" less visible (circuit probably under constrained)

- Still 16.5% saving w.r.t. DVAS @ 8-bit!

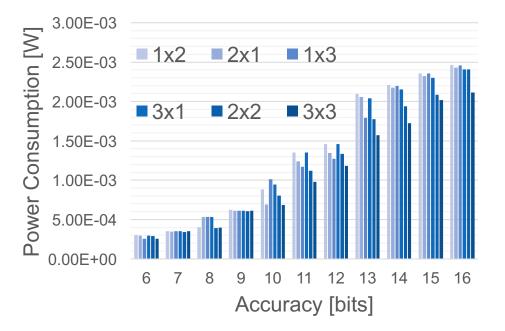

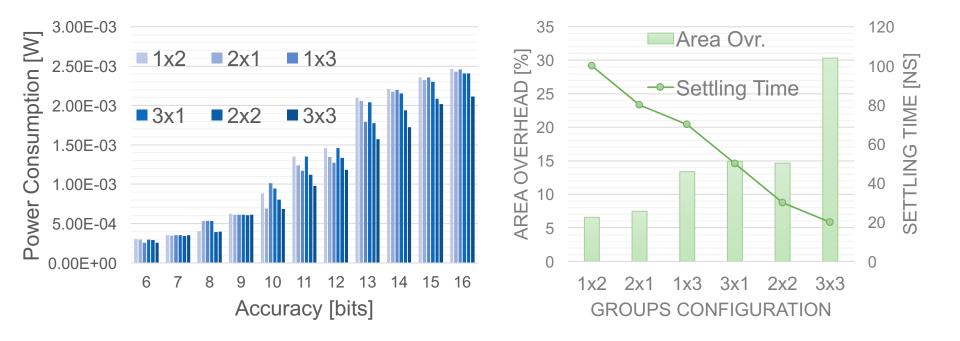

# **Impact of V<sub>BB</sub> Domains**

#### Number of V<sub>BB</sub> domains vs power saving (Booth Mul.):

# Impact of V<sub>BB</sub> Domains

Number of V<sub>BB</sub> domains vs power saving (Booth Mul.):

#### Number of V<sub>BB</sub> domains vs overheads (Booth Mul.):

#### **Conclusions:**

Back-Bias is an effective knob for fine-grain delay/power tuning in quality-configurable functional units.

#### **Conclusions:**

- Back-Bias is an effective knob for fine-grain delay/power tuning in quality-configurable functional units.

- Combined with global V<sub>DD</sub> scaling, this method

overcomes the limitations of DVAS, by contrasting the "Wall-of-slack" phenomenon.

#### **Conclusions:**

- Back-Bias is an effective knob for fine-grain delay/power tuning in quality-configurable functional units.

- Combined with global V<sub>DD</sub> scaling, this method

overcomes the limitations of DVAS, by contrasting the "Wall-of-slack" phenomenon.

- First ever application of Back-Biasing to Quality Configurable Systems (to our knowledge).

#### **Conclusions:**

- Back-Bias is an effective knob for fine-grain delay/power tuning in quality-configurable functional units.

- Combined with global V<sub>DD</sub> scaling, this method

overcomes the limitations of DVAS, by contrasting the "Wall-of-slack" phenomenon.

- First ever application of Back-Biasing to Quality Configurable Systems (to our knowledge).

#### **Future Developments:**

Devise method for runtime update of V<sub>BB</sub> domains configurations depending on operating conditions (PVT, aging, etc.)

#### **Conclusions:**

- Back-Bias is an effective knob for fine-grain delay/power tuning in quality-configurable functional units.

- Combined with global V<sub>DD</sub> scaling, this method

overcomes the limitations of DVAS, by contrasting the "Wall-of-slack" phenomenon.

- First ever application of Back-Biasing to Quality Configurable Systems (to our knowledge).

#### **Future Developments:**

- Devise method for runtime update of V<sub>BB</sub> domains configurations depending on operating conditions (PVT, aging, etc.)

- Investigate alternative partitioning techniques (irregular tiling).

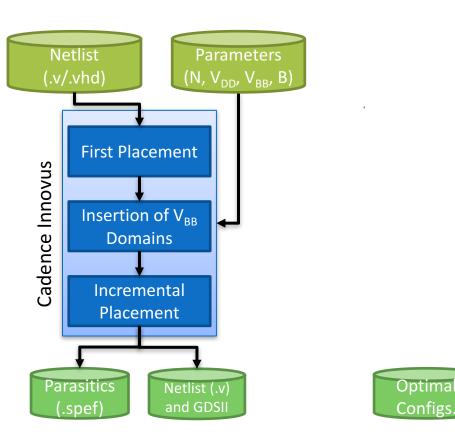

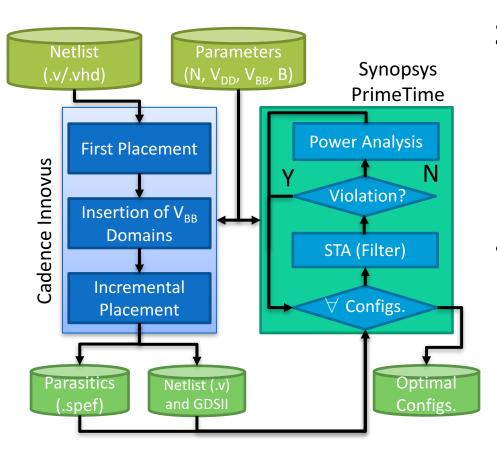

#### **1.** Implementation Phase:

- Partition circuit in VBB domains using regular tiling.

- Incremental placement:

- Insert well-taps

- Fix possible constraints violations due to cell displacement.

# **Implementation Flow**

#### 2. Analysis Phase:

- Exhaustive exploration of all possible configs of Accuracy,  $V_{\rm BB},$  and  $V_{\rm DD}$

- STA to prune unfeasible configurations (timing violations)

- Power analysis on feasible configs

#### Complexity

- Many configurations (thousands), but fast analysis.

- Feasible for < 10-15  $V_{BB}$  domains