#### **Third Italian Workshop on Embedded Systems**

#### Siena – 13-14 September 2018

### **Embedded System Research @UNISI**

#### Roberto Giorgi, Sandro Bartolini, Antonio Rizzo University of Siena, Italy

# http://www.dii.unisi.it/~giorgi

#### Legal Disclaimer:

© 2015-2018 AXIOM Consortium, All Rights Reserved. All other trademarks and copyrights are the property of their respective owners. The list of author does not imply any claim of ownership on the Intellectual Properties described in this document. The authors and the publishers make no expressed or implied warranty of any kind and assume no responsibilities for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information contained in this document. The technology disclosed herein may be protected by one or more patents, copyrights, trademarks and/or trade secrets owned by or licensed to AXIOM Partners. The Partners reserve all rights with respect to such technology and related materials. Any use of the protected technology and related material beyond the terms of the License without the prior written consent of AXIOM and its members and licensors. Until publication, the user should assume that all materials contained and/or referenced in this document are confidential and proprietary unless otherwise indicated or apparent from the nature of such materials (for example, references to publicly available forms or documents). Disclosure or use of this document or any material contained herein, other than as expressly permitted, is prohibited without the prior written consent of AXIOM or such other party that may grant permission to use its proprietary material. The trademarks, logos, and service marks displayed in this document are the registered and unregistered trademarks of AXIOM, whether registered or unregistered, may not be used in connection with any product or service that is not owned, approved or distributed by AXIOM, whether registered or unregistered, may not be used in connection with any product or service that is not owned, approved or distributed by AXIOM, and may not be used in any manner that is likely to cause customer confusion or that disparages AXIOM. Nothing contained in this document should be construed a

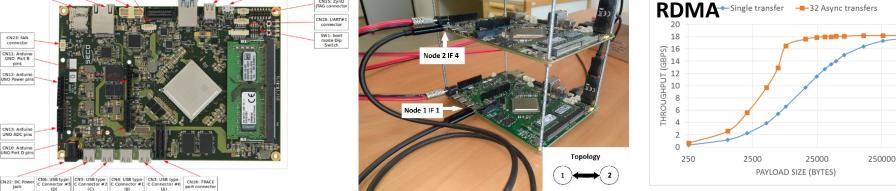

CN9: USB3.0 Jual Type-A Slot CN7: miniDP connector 2015-2018 -- 4Meuro funding Coordinator: Roberto Giorgi

20

16

14 🗒

4

0

#### CNIS: 29/0 CNIS: 29/0 CNIS: Connector CNIS: CANTER CNIS: CONNECTOR CNIS: CANTER CNIS: CONNECTOR CNIS: CNIS: CONNECTOR CNIS: CNIS:

• UNIQUE FEATURES

CN8: RJ-45 Gigabit Ethemet

U16: microSD Card Slot J1: LVDS + T/S connector

- SCALABILITY via USB-C cable: building clusters up to 255 boards

- 4 channels on USB-C cable @ 18Gbps (custom protocol)

- PROGRAMMABILITY via OpenMP: TRANSPARENT FPGA acceleration + CLUSTER distribution

- ARDUINO-UNO socket on board for easy interfacing with the physical world

- > 250MHz Trace port Lauterbach compatible

UPC

Open-source software stack + BSP: <u>https://git.axiom-project.eu/</u> (10<sup>6</sup>+ Lines of Code!)

# http://www.axiom-project.eu/AXIOM\_BOARD\_GUIDE.pdf

EVIDENCE

BSC

Supercomputing

Center

SECO

energia positiva

herta Forth

## **Other projects**

- TERAFLUX: (UNISI=1.3Meuro) 2010-14 <u>http://teraflux.eu</u>

- **ERA: (UNISI=0.4Meuro)** Embedded Reconfigurable Architectures 2010-13

- SARC: Scalable Architectures (UNISI=0.12Keuro) 2005-2010

- ▶ HiPEAC: High Perf. Embedded Arch+Comp. (UNISI=0.06Keuro) 2004-2018

- NCA (FIRB): Non-conventional Architectures (UNISI=0.04Keuro) 2001-2004

- PHOTONICA: Integrated photonics in CMPs (UNISI=0.14Keuro) 2010-2014

- ▶ INASSE: Industry 4.0 As a Service (UNISI=0.15Keuro) 2018-2020

### **Research Group** @ UNISI

- 1 Assoc. prof.: Roberto Giorgi (G) + 1 Aggreg. prof.: Sandro Bartolini (B) + 1 Full Prof. Antonio Rizzo (R):

- Currently 3 PhD Students, 2 Postdocs

- HR Throughput: 2 Full-Prof., 2 Junior Researchers, 9 Postdocs, 10+ PhD students, 20+ students and collaborators ---- during the last 8 years

- Courses (G=Giorgi,B=Bartolini,R=Rizzo):

- (G) Bachelor (L1): **Computer Architecture** (6 credits) -3<sup>rd</sup> year (Italian)

- (G) Master (L2): High Performance Computer Architecture (9 credits) 1<sup>st</sup> and 2<sup>nd</sup> year(English)

- (B) Master (L2): Design of Applications Systems and Services (9 credits) 2<sup>nd</sup> year (English)

- (R) Bachelor (L1): Interaction Design(6 credits) -2<sup>rd</sup> year (Italian)

- (R) Master (L2): Cognitive Science and Tecnology (6 credits) 1<sup>st</sup> year (Italian)

# LAB RESOURCES

#### Lab Resources

- 64-core (x86) CC-NUMA w/1024GiB RAM

- 48-core+256GiB, about 15 simulation servers (8-core+32GiB)

- 12 different FPGA boards ranging from Virtex-6 to Zynq Ultrascale+ (6core 64 bits)

- Xeon Phi, Maxeler Dataflow computer, GPUs, 50+ embedded boards, (20+ workstations)

- Various server machines (Xeon, i7) with up to 128GiB and some hosting high-end Nvidia GPUs: dual 1080ti, 1080, 970

- Intel development suite

- UDOO Lab: 4 kickstarter projects w/SECO

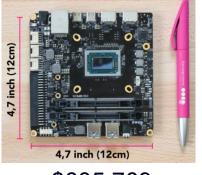

#### 2018, UDOO-BOLT

\$635,769

# Cooperation with Laboratorio Nazionale Embedded Systems and Smart Manufacturing (LN-ESSM) CINI

- CINI lab LN-ESSM (in progress) director prof. Antonino Mazzeo

- UNISI competences

- Giorgi, Bartolini) Programmable Hardware, Processors, Co-processors and Microcontrollers

- (Giorgi) Hardware/software projects ecosystems

- (Giorgi) Smart Cyber-Physical Systems architectures

- (Giorgi, Rizzo) Smart Systems Integration and Internet of Things Applications

- (Rizzo) Human Machine Interface

- (Bartolini) Efficient programmability of heterogeneous multi-/many-core systems with single source code

- (Bartolini) Hardware and software for security, trust, block-chain

- (Bartolini) HW/SW architectures for computer vision

- (Bartolini) Energy Management, power efficiency and approximate computing in embedded nodes

## Scalable Embedded Systems – A new concept?

- ▶ 1 board  $\rightarrow$  ~10s, 2 board(USB-C connected) $\rightarrow$  ~7s (no optimizations)

- SAME board type, SAME software, NO programming efforts, still EMBEDDED

### **Future Directions**

- FPGA/GPU-based Software/Hardware for AI Applications

- Computers for Intelligent Unmanned Systems

- Smart Vision and Security