# Università degli Studi di Sassari IDEA Lab

#### FRANCESCA PALUMBO AND LUCA PULINA

3<sup>rd</sup> Italian Workshop on Embedded Systems (IWES 2018) September 13-14, 2018 – Siena, Italy

## Università degli Studi di Sassari

Established in 1562, UniSS is more than 450 years old.

13,000 students and around 700 scholars. 50+ institutional courses, including 2 international degrees and a wide range of post-graduate activities (PhD courses, advanced training programmes and international exchange projects).

Third medium-sized university by the Italian Censis University Ranking 2015-2016 for services, infrastructure and internationalization.

In 2017 UniSS has obtained the highest co-financing among all the Italian universities for the Erasmus

Traineeship program.

## Intelligent system DEsign and Application (IDEA) Lab - Fundations

Seamless

Х

X

MPSoC

X

X

Energy

X

**Automotive**

**Aerospace**

Healthcare

Consumer

Security

Χ

Certif.

X

Х

Distrib.

X

X

X

Χ

Modern digital devices (*real-time* and *ad-hoc*) are pervasive (*98%* of computers are *embedded*) and may present *sensing and actuating* capabilities.

### **IDEA MISSION**

Optimally implement complex/demanding systems, managing numerous/conflicting requirements

- > CAD for

- Reconfigurable system design;

- Requirements analysis and verification.

- Digital Systems Design

- Low Power System (Multi-Frequency, Clock/Power-Gating);

- Coarse Grained Reconfigurable Accelerators;

- Approximate Computing.

- AI & Formal Methods

- Formal Verification;

- Automated Reasoning;

- Knowledge Representation.

- CAD for

- Reconfigurable system design;

#### Multi-Dataflow Composer (MDC) tool

automatically derive energy efficient coarse-grained reconfigurable accelerators starting from high level dataflow-based functional specifications.

#### http://sites.unica.it/rpct/

**Multi Dataflow** Co-Processo, **Customization of** Generator **Model Based Composer Tool Xilinx-compliant Topology** Structural Profiler accelerators with **Optimization** Dynamic Power Automated Reasoning; related APIs Manager **Coarse-Grained Power Management,** enabling both clock- and power-gating

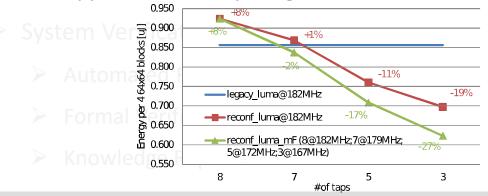

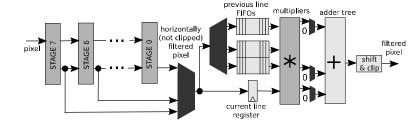

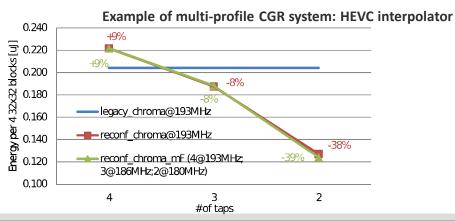

#### Coarse-Grained Reconfigurable Approaches + Functional Approximate Computing

Approximate computing, in conjunction with hardware reconfiguration, guarantees a tunable interpolation system offering an energy versus quality trade-off to further reduce energy.

Sau, C. et al. (2017) " Challenging the Best HEVC Fractional Pixel FPGA Interpolators With Reconfigurable and Multi-frequency Approximate Computing", IEEE ESL

- Digital Systems Design

- Low Power System (Multi-Frequency, Clock/Power-Gating);

- Coarse Grained Reconfigurable Accelerators;

- Approximate Computing.

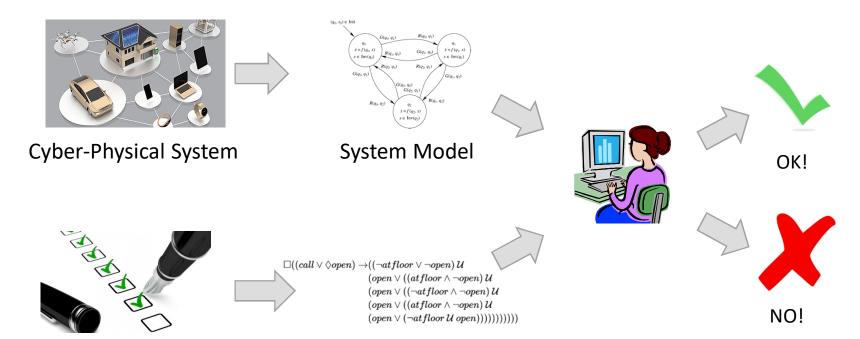

#### AI & Formal Methods

Requirements Goals Logic formalization

## IDEA Lab - People

Luca Pulina

Associate Professor

Francesca Palumbo

Assistant Professor

#### The more the merrier!

Look for open positions at http://idea.uniss.it/index.php/open-positions/

Arthur Bit-Monnot

Postdoctoral Researcher

Laura Pandolfo

Postdoctoral Researcher

Claudio Rubattu Researcher Assistant

Simone Vuotto

Researcher Assistant

Monica Marini

Communication and Administration

## IDEA Lab - On Going Projects

## IDEA Lab - On Going Projects

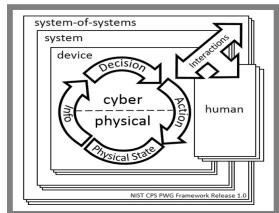

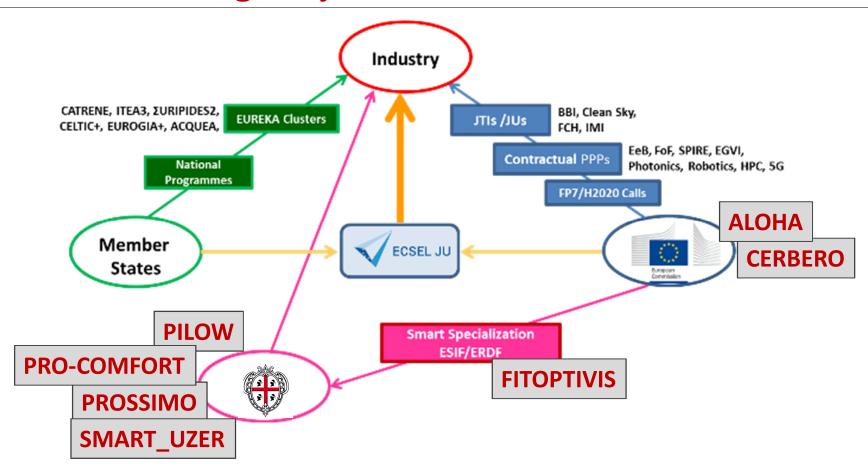

CERBERO – Cross-layer modEl-based fRamework for multi-oBjective dEsign of Reconfigurable systems in unceRtain hybRid envirOnments

H2020 ICT-01-2016 – Duration: 2017-2020 – Role: Scientific Coordinator – Project Value: 5.383.597 € Design environment for Cyber Physical Systems

ALOHA – software framework for runtime-Adaptive and secure deep Learning On Heterogeneous Architectures

H2020 ICT-05-2017 –Duration 2018-2021 – Role: Partner – Project Value: 5.976.415 €

Software development tool flow for Deep Learning on heterogeneous low-energy computing platforms

FITOPTIVIS - From the cloud to the edge: smart Integration and OPtimization Technologies for highly efficient Image and VIdeo processing Systems

H2020-ECSEL-2017 – Duration 2018-2021 – Role: Scientific Coordinator – Project Value: 25.215.007 € Smart integration of image- and video-processing pipelines for Cyber Physical Systems.

## IDEA Lab – On Going Projects

#### PROSSIMO - Progettazione, sviluppo e ottimizzazione di sistemi intelligenti multi-oggetto

POR FESR Sardegna 2014-2020 2014/2020 - Duration: 2018-2020 - Role: Coordinator

Project Value: 284.396 €

Technology transfer: experimentation of innovative methodologies and tools for designing and

verifying Cyber Physical Systems at various stages of the lifecycle.

#### PILOW – Piattaforma Informatica per la LOgistica via Web

P.O. FESR Sardegna 2007-2013, Regione Sardegna – Duration: 2017-2019 – Role: Scientific Coordinator

Project Value: 726.000 €

Develop and experiment innovative solutions in the logistics field.

#### PRO-COMFORT - sistema PRoattivo di Ottimizzazione dell'efficienza energetica e del COMFORT negli edifici

P.O. FESR Sardegna 2014-2020, Regione Sardegna— Duration: 2018-2020 - Role: Scientific Partner

Project Value: 399.656 €

Develop and experiment innovative solutions in the energy management field.

#### SMART\_UzER - Sistema ModulARe e proaTtivo per l'ottimizzazione dell'UtiliZzo dell'Energia elettrica in Reti intelligenti

P.O. FESR Sardegna 2014-2020, Regione Sardegna— Duration: 2019-2021 - Role: Scientific Partner

Project Value: 128.303 €

Development of an intelligent system for energy management.

## IDEA Lab

## Thank you for your attention!

#### **Our contacts:**

Francesca Palumbo: fpalumbo@uniss.it

Luca Pulina: lpulina@uniss.it

Web: <a href="http://idea.uniss.it">http://idea.uniss.it</a>